## 基于 FPGA 的 UART 设计

## 聂 涛1,许世宏2

(1. 空军工程大学 工程学院 陕西 西安 710038; 2. 空军第一航空学院 河南 信阳 464000)

摘 要: UART是一种广泛应用于短距离、低速、低成本通信的串行传输接口。由于常用 UART 芯片比较复杂且移植性差,提出一种采用可编程器件 FPGA 实现 UART的方法,实现了对 UART的模块化设计。首先简要介绍 UART的基本特点,然后依据其系统组成设计顶层模块,再采用有限状态机设计接收器模块和发送器模块,所有功能的实现全部采用 VHDL 进行描述,并用 Modelsim 软件对所有模块仿真实现。最后将 UART 的核心功能集成到 FPGA 上,使整体设计紧凑,小巧,实现的 UART 功能稳定、可靠。

关键词: UART; FPGA; VHDL; 有限状态机; Modelsim

中图分类号: TN915.04 文献标识码: B 文章编号: 1004 - 373X (2006) 02 - 127 - 03

### Design of UART Based on FPGA

NIE Tao<sup>1</sup>, XU Shihong<sup>2</sup>

(1. Engineering Institute, Air Force Engineering University, Xi an, 710038, China; 2. First Aeronautic College of Air Force, Xinyang, 464000, China)

Abstract:UART is a transmission interface widely used in the short — distance, low — speed and low — cost communication Because common UART chip is complicated, this article introduces a method to design UART based on FPGA (Field Programmable Gate Array) and realizes the design of UART models. First, we introduce the basic features of UART, then design the top model based on the system constructers. Second, the receiver and transfer are designed by FSM (Finite State Machine). All functions are given by V HDL. We stimulate the functions with Modelsim successfully, which makes the whole design compact and cabinet, makes UART stable and reliable.

Keywords: UART; FPGA; VHDL; finite - state machine; Modelsim

UART(Universal Asynchronous Receiver Transmitter,通用异步收发器)是广泛使用的串行数据传输协议。UART允许在串行链路上进行全双工的通信。串行外设用到 RS 232 C 异步串行接口,一般采用专用的集成电路即UART实现。如 8250,8251,NS16450 等芯片都是常见的 UART 器件,这类芯片已经相当复杂,有些含有许多辅助的模块(如 FIFO),有时不需要使用完整的 UART的功能和这些辅助功能。那么就可以将所需要的 UART 功能集成到 FPGA 内部,从而简化了电路、减小了体积、提高了可靠性和稳定性,并且具有更大的灵活性。

#### 1 UART 简介

基本的 UART 通信只需要两条信号线 (RXD, TXD) 就可以完成数据的相互通信,接收与发送是全双工形式。 TXD 是 UART 发送端,为输出; RXD 是 UART 接收端,为输入。

UART 的基本特点是:在信号线上共有2种状态,可分别用逻辑1(高电平)和逻辑0(低电平)来区分。在发送器空闲时,数据线应该保持在逻辑高电平状态。发送器是通过发送起始位而开始一个字符传送,起始位使数据

线处于逻辑 0 状态,提示接受器数据传输即将开始。数据位一般为 8 位一个字节的数据(也有 6 位、7 位的情况),低位(LSB)在前,高位(MSB)在后。校验位一般用来判断接收的数据位有无错误,一般是奇偶校验。在使用中,该位常取消。停止位在最后,用以标志一个字符传送的结束,他对应于逻辑 1 状态。

表 1 UART的数据帧格式

| STRAT | D0 D1 D2 D3 D4 D5 D6 D7 | P   | STOP |

|-------|-------------------------|-----|------|

| 起始位   | 数据位                     | 校验位 | 停止位  |

FPGA UART 由 3 个子模块组成:波特率发生器;接收模块;发送模块。如图 1 所示。

图 1 UART 模块组成

#### 2 模块设计

#### 2.1 顶层模块

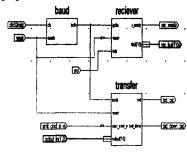

异步收发器的顶层模块由波特率发生器、UART 接收

器和 UART 发送器构成。UART 发送器的用途是将准备输出的并行数据按照基本 UART 帧格式转为 TXD 信号串行输出。UART 接收器接收 RXD 串行信号,并将其转化为并行数据。波特率发生器就是专门产生一个远远高于波特率的本地时钟信号对输入 RXD 不断采样,使接收器与发送器保持同步。

图 2 顶层模块的电路图

图 3 顶层设计与仿真

## 2.2 波特率发生器

波特率发生器实际上就是一个分频器。可以根据给定的系统时钟频率(晶振时钟)和要求的波特率算出波特率分频因子,算出的波特率分频因子作为分频器的分频数。 波特率分频因子可以根据不同的应用需要更改。

图 4 波特率发生器的仿真

## 2.3 UART接收器

由于串行数据帧和接收时钟是异步的,由逻辑 1 转为逻辑 0 可以被视为一个数据帧的起始位。然而,为了避免毛刺影响,能够得到正确的起始位信号,必须要求接收到的起始位在波特率时钟采样的过程中至少有一半都是属于逻辑 0 才可认定接收到的是起始位。由于内部采样时钟bclk 周期(由波特率发生器产生)是发送或接收波特率时钟频率的 16 倍,所以起始位需要至少 8 个连续 bclk 周期的逻辑 0 被接收到,才认为起始位接收到,接着数据位和奇偶校验位将每隔 16 个 bclk 周期被采样一次(即每一个波特率时钟被采样一次)。如果起始位的确是 16 个 bclk 周期长,那么接下来的数据将在每个位的中点处被采样。UART接收器的状态机一共有 5 个状态:

R\_START (等待起始位) 状态 当 UART 接收器复位后,接收状态机将处于这一个状态。在此状态,状态机一直在等待 RXD 的电平跳转,从逻辑 1 变为逻辑 0,即起始位,这意味着新的一帧 UART 数据帧的开始,一旦起128

始位被确定,状态机将转入 R\_CENTER 状态。图 5 中的 RXD\_S YNC 信号是 RXD 的同步信号,因为在进行逻辑 1 或逻辑 0 判断时,不希望检测的信号是不稳定的,所以不直接检测 RXD 信号,而是检测经过同步后的 RXD\_S YNC 信号。

R\_CENTER (求中点) 状态 对于异步串行信号,为了使每一次都检测到正确的位信号,而且在较后的数据位检测时累计误差较小,显然在每位的中点检测是最为理想的。在本状态,就是由起始位求出每位的中点,通过对bclk 的个数进行计数 (RCNT16),但计数值不是想当然的"1000",要考虑经过一个状态,也即经过了一个bclk周期,所希望得到的是在采样时 1/2 位。另外,可能在R\_START 状态检测到的起始位不是真正的起始位,可能是一个偶然出现的干扰尖脉冲(负脉冲)。这种干扰脉冲的周期是很短的,所以可以认为保持逻辑 0 超过 1/4 个位时间的信号一定是起始位。

R\_WAIT (等待采样) 状态 当状态机处于这一状态,等待计满 15 个 bclk,在第 16 个 bclk 是进入 R\_SAM-PLE 状态进行数据位的采样检测,同时也判断是否采集的数据位长度已达到数据帧的长度(FrameLen),如果到来,就说明停止位来临了。FrameLen 在设计时是可更改的(使用了 Generic),在本设计中默认为 8,即对应的UART 工作在 8 位数据位、无校验位格式。

$R_{-}$  SAMPLE (采样) 状态 即数据位采样检测,完成后无条件状态机转入  $R_{-}$  WAIT 状态,等待下次数据位的到来。

$R_STOP$  状态(停止位接收) 无论停止位是 1 位还是 1.5 位,或是 2 位,状态机在  $R_STOP$  不具体检测 RXD,只是输出帧接收完毕信号( $REC_DONE < = 1$ ),停止位后状态机转回到  $R_START$  状态,等待下一个帧的起始位。

图 5 接收器状态机

图 6 接收器仿真

#### 2.4 UART 发送器

发送器只要每隔 16 个 bclk 周期输出 1 个数据即可,次序遵循第 1 位是起始位,第 8 位是停止位。在本设计中没有校验位,但只要改变 Generic 参数 FrameLen,也可以

加入校验位,停止位是固定的 1 位格式。发送状态机一共有 5 个状态:

X\_IDLE (空闲) 状态 当 UART 被复位信号复位后,状态机将立刻进入这一状态。UART 的发送器一直在等待一个数据帧发送命令 XMIT\_CMD。XMIT\_CMD\_P信号是对 XMIT\_CMD 的处理,XMIT\_CMD\_P是一个短脉冲信号。XMIT\_CMD 进行了脉冲宽度的限定,当 XMIT\_CMD P= 1,状态机转入 X START,准备发送起始位。

$X_START$ (起始位)状态 在这个状态下,UART 的发送器一个位时间宽度的逻辑 0 信号至 TXD,即起始位。紧接着状态机转入  $X_WAIT$  状态。XCNT16 是 bclk 的计数器。

X<sub>WAIT</sub> (移位等待) 状态 同 UART 接收状态机中的 R WAIT 状态类似。

图 7 发送器状态机

X SHIFT (移位) 状态 当状态机处于这一状态时,

实现待发数据的并串转换。转换完成立即回到  $X_-$  WAIT 状态。

$X_STOP$  (停止位) 状态 停止位发送状态,当数据帧发送完毕,状态机转入该状态,并发送  $16 \land bclk$  周期的逻辑 1 信号,即 1 位停止位。状态机送完停止位后回到  $X_IDLE$  状态,并等待另一个数据帧的发送命令。

图 8 发送器仿真

### 3 结 语

利用 Modelsim 对 Xilinx 公司的 FPGA 芯片 Spartan 系列器件完成仿真,结果稳定可靠。该设计具有极大的灵活性,具有一定的参考价值。

## 参 考 文 献

- [1] 侯伯亨, 顾新. V HDL 硬件描述语言与数字逻辑电路设计 [M]. 西安: 西安电子科技大学出版社, 1999.

- [2] 黄海林,沈绪榜.基于有限状态机 UART 设计 [J].微电子学与设计,2002,19(12):52-55.

- [3] 张莉,杨永明.基于 CPLD 的 UART 设计 [J]. 微计算机信息,2002,2 (18):60-61.

作者简介 聂 涛 男, 1982 年出生, 硕士研究生。研究方向为通信与信息系统。 许世宏 男, 1963 年出生, 教授。研究方向为通信与信息系统。

# 国资委建议发展 3 G应优先支持 TD - SCDMA

国资委专家近日在此间表示,中国优先支持具有自主知识产权的 TD - SCDMA (中国提出的 3 G 国际标准),有利于在 3 C 技术和产品融合的新一轮技术革命中赢得主动,有利于真正占领世界科技竞争的制高点。

国资委研究中心新产业研究部副部长卢奇 骏在五日的二 00 六中国通信经济年会上表示,中国对于国外的 3 G技术已经积极跟进,并做了全球最大规模的试验,现在进入培育市场阶段,而培育市场势必要发 3 G 牌照。

此前 2005 年 12 月底信息产业部的高层官员 也曾表示,中国发展 3 G 的时机已经成熟,二 00 六年将制定出技术、资费等 3 G 相关政策。

卢奇骏认为中国提出的 3G 国际标准应该得

到强有力的政策支持。由于 TD - SCDMA 本身没有经过产业化,存在一定的投资风险,因而使运营商对发展 TD - SCDMA 有顾虑。他认为国家每年用于技术创新的财力非常有限,建立新的投资体制很有必要。

卢奇骏认为,在专利费方面,中国在 2 G 时代付出了巨大的成本。如果 3 G 的标准掌握在自己的手里,则不用付那么高的专利费,专利费低的结果是企业可以有更多的盈利用于技术研发,用于设备的更新、改造,会有大的发展潜力,有利于中国电信产业的发展。

国资委是大型国有企业的主要主管部门, 业内人士认为,国资委在3G政策上亦有一定的 发言权。